ARM每年都會發布新一代的IP核心,只是今年誕生的Cortex-X2、Cortex-A710和Cortex-A510有些特殊,因為它們是第一批基於ARMv9指令集打造的消費端IP(適用於資料中心的Neoverse N2釋

2021-07-16 03:02:24

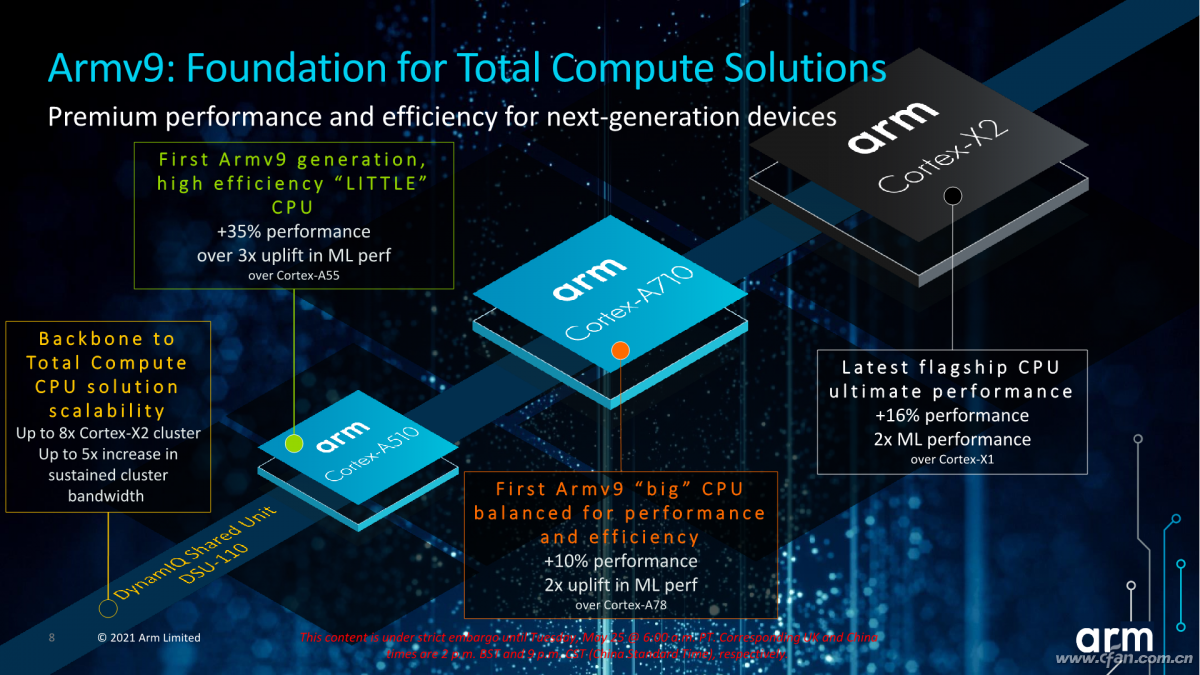

ARM每年都會發布新一代的IP核心,只是今年誕生的Cortex-X2、Cortex-A710和Cortex-A510有些特殊,因為它們是第一批基於ARMv9指令集打造的消費端IP(適用於資料中心的Neoverse N2釋出更早)。

其中,Cortex-X2是ArmV9指令集架構中的「皇帝」,扮演SoC移動平臺裡的「超大核」角色。它通過將分支預測與預取單元解耦分離、減少流水線長度、增加亂序執行視窗和載入儲存視窗的數量以增強資料預取能力等方式,較之上代Cortex-X1在整數效能(IPC)方面提升16%,機器學習效能(ML)則可以翻一番,同時還擁有更好的能效比表現。

注意參與對比的Cortex-X1僅配備4MB三級快取,而真正滿血的Cortex-X1也是支援8MB三級快取的

Cortex-A710通過改進分支預測、提升預取增強功能、優化核心與DSU聯絡等方式,在同製程工藝和頻率的情況下,相比Cortex-A78的IPC效能提升10%,或者可以將功耗降低30%,機器學習效能也可得以翻倍。

Cortex-A510借鑑了Cortex-X系列在分支預測、資料預取方面的一些技術,而且還引入了一種名為「融合核心」的微架構,相比前輩Cortex-A55可提升35%~62%的效能,機器學習效能更是提升了3倍。

需要注意的是,上述效能提升都存在一定的水分。比如,Cortex-X2的16%效能增益,是建立在滿血8MB三級級緩的基礎上;Cortex-A710和Cortex-A510要想滿血釋放效能,理論也需要搭配4MB二級快取和8MB三級快取(A710),以及32KB、256KB和8MB的一級、二級、三級快取(A510)。然而,現實中晶片商很難將料「堆滿」。

實際上,驍龍、天璣、麒麟等擁有相同工藝、架構和主頻的晶片間之所以還存在效能上的差異,很大程度就是快取容量的大小有別引起的。

而晶片商之所以鮮有搭配滿血ARM IP架構核心設計的原因,就是受制於摩爾定律的放緩——哪怕採用了最先進的5nm製程工藝,以驍龍888為代表的旗艦級晶片還是存在發熱高、功耗大的缺陷,很多驍龍888手機在玩《原神》級別遊戲時的體驗反而不如一些搭載驍龍870的次旗艦,是不是很驚喜?

在ARM最新的一篇部落格文章中,企業院士兼技術總監Rob Aitken就表示,如今摩爾定律遇阻,在工藝縮排到原子尺度時,ARM需要重新調整下產品努力的方向,更多去關注每瓦效能的改進。

換句話說,未來ARM的IP核心,將不再著重於IPC效能的提升,而將更加看重能效比的改進——擠牙膏的時代即將來臨,大家做好心理準備吧。

相關文章

ARM每年都會發布新一代的IP核心,只是今年誕生的Cortex-X2、Cortex-A710和Cortex-A510有些特殊,因為它們是第一批基於ARMv9指令集打造的消費端IP(適用於資料中心的Neoverse N2釋

2021-07-16 03:02:24

AMD Zen CPU、RDNA GPU都是極為優秀的架構,能效超高,也得到了不少遊戲掌機的青睞。今天,Vavle正式釋出了他們的遊戲掌機「Steam Deck」(之前傳聞名為Stream Pal),配備的正是AMD

2021-07-16 03:02:10

自拍並不是什麼新鮮概念,1999年世界上首款支援拍照的手機就只有前置攝像頭。放到現在單純的自拍就更不是什麼亮點了。現在的前置相機,講究的是「人像」模式。「人像」一詞最早

2021-07-16 03:00:13

熱門數碼科技資訊早知道,快來關注作者。編輯|孫鳳新稽核|文崢近日,網路上流出一組關於iPhone 13 Pro系列的渲染圖,配色包括了一直沿用的黑、白,還有新增的黃銅色以及玫瑰金色。有

2021-07-15 03:18:16

華為跌倒之後,蘋果、三星成為了高階市場中僅有的兩位重量級玩家。日前有外媒報道,蘋果正在尋求2021年的iPhone13系列產量增加20%,生產出多達9000萬部的iPhone13。而在往年,iPhon

2021-07-15 03:18:11

周世鐵,微醫前端技術部醫療支撐組前端亂構師前言在我們編寫業務程式碼的時候,可能很少人會使用到AST,以至於大多數同學都不大瞭解AST。有的同學曾經學過,但是不去實踐的話,過段時

2021-07-15 03:17:58